PSI6504MP IP Brief

Description:

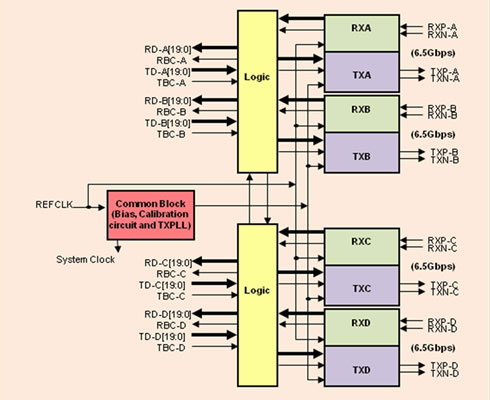

PSI6504MP is a 4 channel multi-protocol SERDES with each channel

capable of operating up to 6.5Gbps. PSI6504MP can provide interfaces

for many applications including XAUI (10G Attachment Unit

Interface), RXAUI (10G Reduced Attachment Unit Interface), SGMII

(Serial Gigabit Media Independent Interface), SFI4.2, SFI5.1 (Serdes

Framer Interface level 4 and 5) and HRIF. Fig. 1 shows the top-level

block diagram of this module. Depending on the application, each

transmitter can serialize 8, 10, 16 or 20 bit parallel data to a

differential serial output and each receiver can de-serialize a

differential serial input to 8, 10, 16 or 20 bit parallel output. A

common block including a TXPLL provides clocks to the serializers in

all channels. To improve signal integrity the common block also

includes a calibration circuit providing control signals to make the

transmitter output resistance and the receiver input resistance

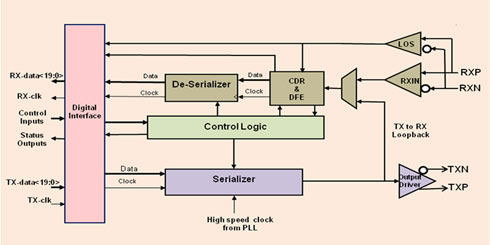

within 50Ω±5%. Fig. 2 shows the simplified block diagram of each

channel. At the RX side the serial input data goes through the input

stage with linear equalization. The Clock and data recovery (CDR)

circuit receives the data. It then extracts the clock, and provides

the clock and the retimed data to the de-serializer. The de-serializer

converts the serial data to 8, 10, 16 or 20bit parallel data with

corresponding rx-clk. A DFE (Decision Feedback Equalization) block

has been implemented in this module, and for the cases where a

higher jitter tolerance is required, it is enabled. A Loss Of Signal

(LOS) detector detects if there are valid data at the input. At the

TX side the serialized data goes through the output driver. To

further improve the jitter performance there are programmable

pre-emphasis capabilities at the transmitter output stage. In

addition near end and far end serial loopback are implemented to be

able to test the channel.

Features:

- 4 channel SERDES capable of operating at 1.1-1.625, 2.2-3.25 and 4.4-6.5Gbps.

- Jitter generation and jitter tolerance exceed the specifications for many applications such as XAUI, RXAUI, SGMII, SFI4.2, SFI5.1 and HRIF.

- Serial output driver with calibrated on-chip termination resistor.

- Selectable pre-emphasis level of signal at the output driver.

- Serial input receiver with calibrated on-chip termination resistor.

- Fixed equalization capability at the receiver input.

- Decision Feedback Equalization (DFE)

- Near end and far end serial loopback.

- Loss of signal detector.

- Eye monitor.

- AC JTAG

- Reference clock can be between 60MHz to 800MHz.

- 2 power supplies of 0.9V and 1.2V.

- Only one external component is used (external resistor for termination resistor calibration).

- TSMC 40nm G process.

Fig. 1 Top level block diagram

Fig. 2 Simplified block diagram of TX/RX block